差分线传输的理解

想请教各位,差分线传输要求要紧密耦合,那会不会引起串扰呢? 会引起串扰的,所以差分对一定要进行匹配, 耦合的越紧,对匹配的要求越大。 在做到良好的匹配的同时,耦合的越紧密,它们对外界的抗干扰越强 因为外界干扰对它们的影响是同时的,而差分对关注的是两个信号的差别,所以对外界的共模噪声免疫。 串扰是当信号发生跳变的时候由于线间的耦合电容耦合过来的,那差分对的匹配是什么原理来消除串扰?具体说明有吗? 匹配是通过消除反射来减小串扰的影响,但不是消除串扰 差分对之间既然存在电容和电感的耦合,那么理论上也存在串扰, 前向串扰和后向串扰的反射是接受端受到的主要影响,前向串扰由于容性和感性耦...

相关推荐

-

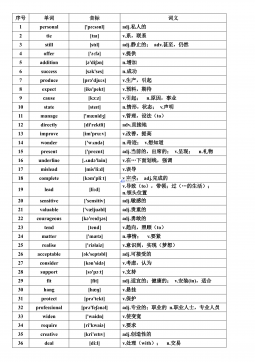

【词汇变形总汇】2025高考词汇变形总汇 - 教师版VIP免费

2024-12-06 6

2024-12-06 6 -

【超简37页】新课标高考英语考纲3500词汇VIP免费

2024-12-06 18

2024-12-06 18 -

《高考英语3500词详解》(WORD版)VIP免费

2024-12-06 33

2024-12-06 33 -

《高考英语3500词详解》VIP免费

2024-12-06 29

2024-12-06 29 -

高中英语-[教师版]80天通关高考3500词汇VIP免费

2024-12-06 33

2024-12-06 33 -

高中人教选修7课文逐句翻译VIP免费

2024-12-06 14

2024-12-06 14 -

高中人教选修7课文原文及翻译VIP免费

2024-12-06 40

2024-12-06 40 -

高中人教必修4课文逐句翻译VIP免费

2024-12-06 31

2024-12-06 31 -

高中人教必修4课文原文及翻译VIP免费

2024-12-06 58

2024-12-06 58 -

高考英语核心高频688词汇VIP免费

2024-12-06 34

2024-12-06 34

作者详情

相关内容

-

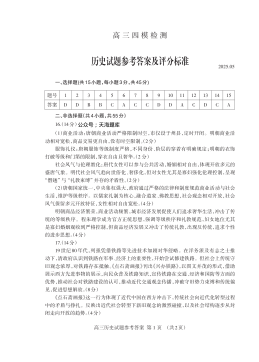

山东省泰安市2025届高三四模检测历史答案

分类:中学教育

时间:2026-03-20

标签:无

格式:PDF

价格:10 玖币

-

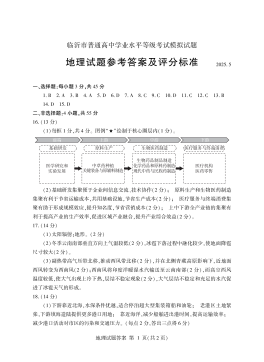

山东省临沂市普通高中学业水平等级考试模拟试题地理答案

分类:中学教育

时间:2026-03-20

标签:无

格式:PDF

价格:10 玖币

-

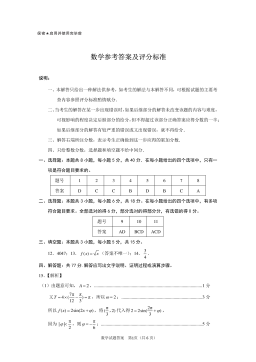

山东省临沂市2025届高三上学期教学质量检测考试暨期中考试(九五联考)数学答案

分类:中学教育

时间:2026-03-20

标签:无

格式:PDF

价格:10 玖币

-

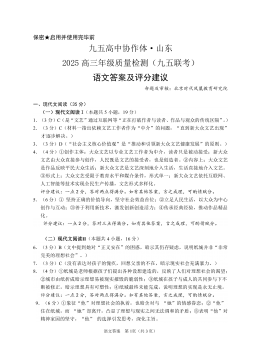

山东省九五高中协作体2025高三年级质量检测(九五联考)语文答案

分类:中学教育

时间:2026-03-20

标签:无

格式:PDF

价格:10 玖币

-

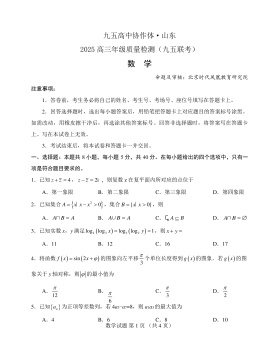

山东省九五高中协作体2025高三年级质量检测(九五联考)数学

分类:中学教育

时间:2026-03-20

标签:无

格式:PDF

价格:10 玖币

渝公网安备50010702506394

渝公网安备50010702506394