电子技术数字电子技术基础第 6 章 时序电路的分析与设计

第6章时序电路的分析与设计第6章时序电路的分析与设计6.1时序电路概述6.2同步时序逻辑电路的分析6.3异步时序电路的分析方法6.4同步时序电路的设计方法第6章时序电路的分析与设计6.1时序电路概述6.1.1时序电路的特点逻辑电路分为两类:一类是组合逻辑电路,另一类是时序逻辑电路。在组合逻辑电路中,任一时刻的输出仅与该时刻输入变量的取值有关,而与输入变量的历史情况无关;在时序逻辑电路中,任一时刻的输出不仅与该时刻输入变量的取值有关,而且与电路的原状态,即与过去的输入情况有关。第6章时序电路的分析与设计图6-1时序逻辑电路的结构框图与组合逻辑电路相比,时序逻辑电路有两个特点:第一,时序逻辑电路包...

相关推荐

-

Michael Moorcock - Elric 6 - StormbringerVIP免费

2024-12-08 19

2024-12-08 19 -

Michael Crichton - PreyVIP免费

2024-12-08 22

2024-12-08 22 -

Mercedes Lackey - WintermoonVIP免费

2024-12-08 19

2024-12-08 19 -

Mercedes Lackey - SE 1- Born To RunVIP免费

2024-12-08 18

2024-12-08 18 -

Mercedes Lackey - Heralds of Valdemar 1 - Arrows Of The QueeVIP免费

2024-12-08 23

2024-12-08 23 -

Melville, Herman - TypeeVIP免费

2024-12-08 29

2024-12-08 29 -

MaryJanice Davidson - [Betsy 5] - Undead and Unpopular (v1.0)VIP免费

2024-12-08 34

2024-12-08 34 -

Marion Zimmer Bradley - Darkover - The Heirs of HammerfellVIP免费

2024-12-08 38

2024-12-08 38 -

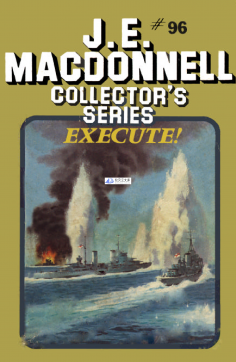

MacDonnell, J E - 096 - Execute!VIP免费

2024-12-08 23

2024-12-08 23 -

Lovecraft, H P - The Dream Quest Of Unknown KadadthVIP免费

2024-12-08 40

2024-12-08 40

作者详情

相关内容

-

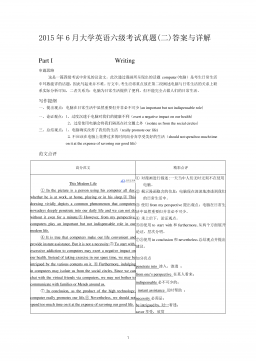

2015年6月英语四级真题答案及解析(卷二)

分类:外语学习

时间:2025-05-02

标签:无

格式:PDF

价格:5.8 玖币

-

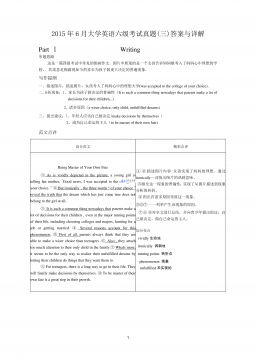

2015年6月英语四级真题答案及解析(卷三)

分类:外语学习

时间:2025-05-02

标签:无

格式:PDF

价格:5.8 玖币

-

2016年12月六级(第二套)真题

分类:外语学习

时间:2025-05-02

标签:无

格式:PDF

价格:5.8 玖币

-

2016年12月六级(第三套)真题

分类:外语学习

时间:2025-05-02

标签:无

格式:PDF

价格:5.8 玖币

-

2016年12月六级(第一套)真题

分类:外语学习

时间:2025-05-02

标签:无

格式:PDF

价格:5.8 玖币

渝公网安备50010702506394

渝公网安备50010702506394